Micro-Computer Design

Field

PCB design

Institution

Letourneau University

Year

2022

Project Type

Individual

Course

MCD

Keywords

SBC, RAM, ROM, CPU, CPLD, Duart, VHDL, Assembly language, FPGA, Supervisor Chip, Logic Analyzer, Memory Mapping, S-record, Hardware-Software Integration

This project embarked on the ambitious task of designing and constructing a single board computer from the ground up, incorporating essential components such as RAM, ROM, CPU, CPLD, and Duart. The core of the device's logic and decoding mechanisms were developed using VHDL, while the monitor program was intricately coded in 68000 assembly language. The hardware architecture adheres to specified requirements, featuring a comprehensive setup with dual ROM and RAM configurations, a CPLD for programmable logic, a CPU for processing, and a Duart for serial communication, all powered through a stabilized 9V to 5V regulation system. Despite challenges and minor modifications to the initial design, the project maintained its functional integrity. On the software front, a monitor program was created to provide a user interface that allows interaction with the system through a simple menu, demonstrating basic input and control features. This endeavor showcases not just a deep dive into hardware assembly and software integration, but also a commitment to bridging the gap between conceptual knowledge and practical application in computer engineering.

Hardware Overview

This section of the project outlines the meticulous design and assembly of a single board computer, conforming to specific educational standards and incorporating a comprehensive array of components to achieve optimal functionality and performance. This comprehensive setup not only demonstrates a deep understanding of computer engineering principles but also highlights the importance of precision in component selection and circuit design for the successful implementation of a single board computer.

-

Designed to meet instructor-specified requirements.

-

Includes a CPU, CPLD, Duart, RS232 driver, two sets of ROM and RAM, and a 9V to 5V power system using a voltage regulator.

-

Utilizes 14 1uF capacitors to stabilize voltage and prevent spikes.

hardware block diagram

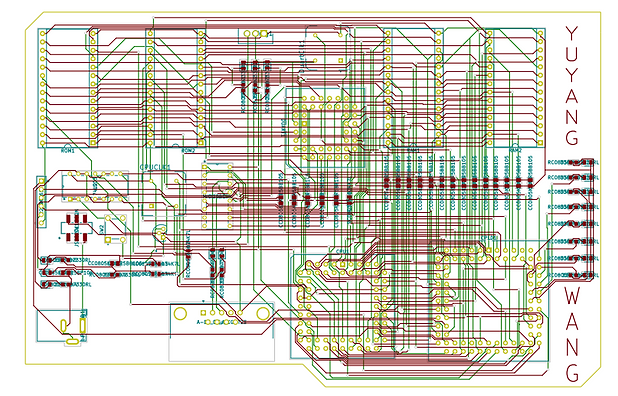

board layout

schematics

Key Points of the Hardware Configuration

-

Component Assembly: The system integrates critical computing elements—CPU for processing, CPLD for complex programmable logic, Duart for serial communication, and RS232 drivers for standard serial communication protocol.

-

Memory Units: Features two ROMs (upper and lower) and two RAMs (upper and lower) for a robust memory architecture.

-

Power Management: Employs a 9V barrel jack input with a voltage regulator to ensure a stable 5V power supply.

-

Circuit Stability: Incorporates capacitors between ground and VCC to mitigate voltage fluctuations.

-

Design Fidelity: The final board closely aligns with the initial schematic, albeit with minor modifications for optimization.

-

LED Utilization: Some LEDs were removed due to soldering issues or non-functionality, which did not impact the board's operational capabilities.

-

Component Selection: Adhered to a mix of provided CPLD and CPU specifications, along with researched components like RAM, ROM, RS232 drivers, and Duart, based on industry standards and previous project insights.

-

Reset Mechanism: Adjustments made to the reset button for accurate footprint alignment.

Software Description

This section of the project delves into the software architecture of a monitor program designed for a custom single board computer, detailing its functionality, user interaction, and memory management. This software framework highlights a focused approach to creating a functional monitor program, balancing between essential features and the potential for future development to enhance its capabilities further.

-

User Interface: Initiates with a title page for visual engagement, leading to a main menu for function selection.

-

Functionality: Users can execute commands in any sequence, with the system designed to return to the main menu upon completion of tasks.

-

Error Handling: Implements input checks to prevent and notify of incorrect entries, advising board reset to address errors.

-

Memory Mapping: Showcases memory allocation, with ROM reserved for the monitor program and RAM for read/write operations, including Duart communication beyond specific memory thresholds.

-

Core Code Operations: Supports essential functions like memory read/write, register manipulation, and S-record loading, specifically tailored for S1 type records.

-

Input Processing: Converts ASCII Hex input into Hex format for effective data handling, utilizing memory locations for translating and storing commands.

-

Future Enhancements: Acknowledges current limitations due to hardcoded elements, with aspirations for future refinements to optimize RAM usage and expand functionality.

software logic flow chart

Troubleshooting Skills Demonstrated

This section showcases the methodical troubleshooting process undertaken during the development of a complex single board computer project, highlighting the problem-solving skills and technical acumen employed to address various challenges. This narrative emphasizes a structured approach to diagnosing and rectifying hardware and software issues, underscoring a persistent dedication to project success despite initial setbacks. The ability to navigate through complex problems, apply critical thinking, and implement effective solutions illustrates a high level of engineering expertise and a proactive troubleshooting methodology.

-

Power System Analysis: Identified and resolved a short circuit in the power system caused by a surface-mounted capacitor, showcasing meticulous component examination and problem isolation capabilities.

-

Reset Circuit Refinement: Addressed issues with the reset circuitry and supervisor chip through a series of logical deductions and hardware modifications, eventually streamlining the reset mechanism to ensure reliable CPU initialization.

-

CPLD Debugging: Overcame challenges with the CPLD, including outdated software tools and a faulty pin, through systematic testing and code verification, leading to successful programming and operational validation.

-

Memory and Communication Tests: Corrected test code anomalies and hardware setup errors to successfully pass RAM and Duart functionality tests, demonstrating a deep understanding of memory addressing and system integration.

This project embarked on the ambitious creation of a single board computer, integrating a suite of complex components including RAM, ROM, CPU, CPLD, and Duart. Through a journey that spanned from conceptual design to hardware assembly and software development, the endeavor showcased the intricate process of bringing a sophisticated computing device to life. Utilizing VHDL for hardware description and assembly language for the monitor program, the project not only adhered to but also expanded upon the foundational requirements set forth. Throughout the development, a series of methodical troubleshooting and refinements were undertaken to address challenges in power systems, reset circuit configurations, CPLD functionality, and memory testing. These efforts underscored the critical importance of resilience, technical acumen, and a systematic approach to problem-solving within the realm of computer engineering. In conclusion, this project stands as a testament to the practical application of FPGA systems, from basic data handling and storage to the complexities of automated testing and hardware-software integration. It highlights the potential for innovation and the depth of knowledge required to navigate the challenges inherent in designing and implementing advanced technological solutions.